Incluso con reductor de focal la cámara pasa por la horquilla de un S/C.

CG-3: TERCERA PARTE

|

Incluso con reductor de focal la cámara pasa por la horquilla de un S/C. |

El estado actual de la cámara es casi definitivo desde el punto de vista hardware. En el camino han surgido nuevas ideas, algunas se han perfeccionando y otras han desaparecido. Finalmente la cámara consta de dos tarjetas alojadas en el cabezal y una fuente de alimentación externa. En la tarjeta de mayor tamaño se encuentra toda la circuiteria digital y en la menor la parte analógica. Esta modularidad permitirá cambiar el modulo analógico fácilmente si las circunstancias lo requieren, por ejemplo para cambiar a otro conversor A/D y aumentar la velocidad de adquisición.

En el software, la situación está si cabe mejor. Se está encargando de él Rafael González, un fichaje de lujo. Ahora somos un equipo..... ya podemos jugar al futbolín.

El principal cambio ocurrido hasta el momento reside en la utilización de lógica programable. Cuando ya tenia funcionando todos los circuitos digitales, se me presentó la oportunidad de usar esta poderosa tecnología que es la lógica programable. Ha implicado bastante retraso. Hay que aprender a manejar un entorno de desarrollo nuevo y complejo, pero además de reducir el tamaño del circuito impreso a un cuarto o más, las posibilidades para el futuro son tremendas. Gracias a este dispositivo, la mayoría de los circuitos digitales de la cámara podrán ser modificados o ampliados sin tan siquiera tener que abrir la caja. Las modificaciones o actualizaciones del hardware se realizaran a través del puerto serie de la cámara. La placa principal será más universal que nunca.

El chip empleado en este caso es una FPGA (Field Programable Gate Array) de Xilinx, la XC4005E. Tiene 84 terminales y 5000 puertas lógicas. Si el esquema creciera demasiado, solo hay que sustituirlo por otro de mayor capacidad.

La cámara en el proceso final de diseño con el analizador lógico conectado a la FPGA.

La placa pequeña contiene los circuitos analógicos

Para que todos podamos entenderlo, podríamos decir que la FPGA es una caja en cuyo interior hay varios miles de puertas lógicas y una memoria. Según el código que carguemos en esa memoria, determinaremos las conexiones entre esas puertas y por tanto dentro de la FPGA podremos "programar" cualquier circuito digital, por complejo que sea.

Un ejemplo. La comunicación con el PC actualmente se efectúa por el puerto de impresora en modo SPP para compatibilizar con los ordenadores más viejos. Si más adelante se desea usar el puerto en modo EPP, habrá que modificar el circuito. Pero estas modificaciones se realizaran dentro de la FPGA, por lo que físicamente no habrá que tocar la placa. Solo habrá que cargar el código correspondiente.

Hasta ahora, el puerto de impresora, se ha considerado como la opción más universal y rápida. Todos los ordenadores, viejos y nuevos, portátiles y de sobremesa lo tienen. Pero actualmente ya existen otras formas de conexión. Es seguro que el USB terminará imponiéndose. Pues bien, gracias a la FPGA, llegado el momento y una vez desarrollado el circuito correspondiente, podremos incluir en la cámara el puerto USB.

Tanto el programa del microprocesador como el código de la xilinx residen en memoria FLASH. El código de la FPGA es cargado en esta por el microprocesador cada vez que arranca la cámara, para configurarla con el circuito que estemos usando.

Configuración final de la cámara.

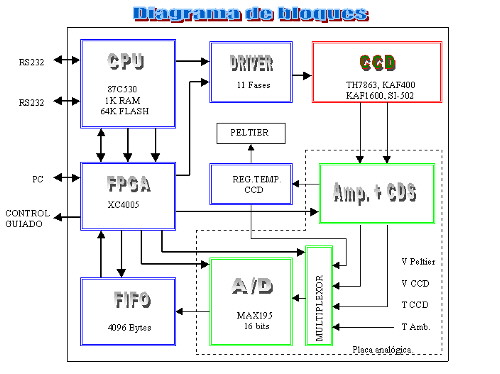

En el siguiente diagrama funcional puede verse como queda finalmente el circuito.

CPU: está compuesta por el microprocesador funcionando a 22Mhz y una memoria Flash. La ROM interna del micro aloja un programa encargado del arranque de la cámara. Es el encargado de almacenar en la Flash él autentico programa operativo usando un puerto serie. La CPU controla casi todas las funciones de la cámara a través de la FPGA. De forma directa puede generar hasta ocho fases de control para el CCD y dispone de dos puertos serie. Uno de estos puertos es imprescindible para las actualizaciones. En condiciones normales los dos quedan disponibles. Su uso dependerá de las necesidades particulares y de futuras ampliaciones. Inicialmente uno estará dedicado a manejar el enfoque desde el programa de adquisición. El otro actualmente se está usando como terminal para debuguer, mostrando en un terminal el estado de la cámara, admitiendo además ordenes sin necesidad del programa de adquisición.

Diagrama de la cámara por bloques

FPGA: de cara al exterior, contiene la comunicación con el puerto paralelo y cuatro líneas de control que podrán permitir por ejemplo funciones de guiado.

Sin duda, el circuito más interesante contenido en este chip es el secuenciador. Su misión es generar diez señales de control muy rápidas. De ellas tres, son fases del CCD, cinco son para el doble S/H y conversor A/D, una para escribir en la FIFO y la ultima para interrumpir al micro al acabar la tarea.

Para conseguir esto, el secuenciador dispone de dos bancos de RAM donde el micro, puede cargar en cualquier momento dos posibles secuencias que dependerán del modo de exploración, del bining, etc. A una orden de la CPU se inicia el barrido de la RAM que ira generando las señales. Existe otro registro donde se carga el numero de veces que se debe repetir la secuencia seleccionada. La velocidad a que se generan estas señales es determinada por un reloj también programable procedente de la CPU. Para indicar el final del ciclo programado se genera una interrupción. De esta forma la CPU queda liberada del trabajo más intenso y puede dedicarse a otras funciones.

Otra función incluida en la FPGA es generar una señal PWM destinada a regular la temperatura del CCD.

FIFO: es una memoria que hace de buffer entre la cámara y el PC. En ella se puede almacenar la lectura de varias líneas. Se consigue que la tarea de lectura del puerto paralelo por parte del PC no sea critica. Se simplifica el programa de adquisición y se gana en velocidad, gracias a que el PC puede leer la imagen por bloques de varias líneas.

DRIVER: este bloque es muy sencillo, simplemente pasa las señales TTL a los niveles CMOS requeridos por el CCD. Son circuitos del tipo DS0026.

REG. TEMP. CCD: es la etapa de potencia para la regulación de temperatura.

PLACA ANALÓGICA: contiene el amplificador de salida del CCD, el doble S&H, un multiplexor analógico para seleccionar las diferentes señales a medir, y el conversor A/D. Tambien contiene la adaptación de la salida PWM de la FPGA y el modulo de potencia para la regulación de temperatura.

Mesa de trabajo en la recta final. Dos herramientas muy necesarias:

Un osciloscopio digital y en el portátil un pequeño analizador lógico.

En el PC el programa de adquisición.

Coslada 1-agosto-1999